# EM78XXX 15-Bit Instruction Set Application Notes

# 1 Instruction

EM78xxx is a RISC-like single chip microcontroller. Each instruction is a 15-bit word divided into an OP code and one or more operands. All instructions are mostly executed with single instruction cycle, unless the program counter is changed by executing the "MOV R2, A", "ADD R2, A", "LCALL", or "LJMP" instruction. In this case, the execution takes two instruction cycles.

In addition, the EM78xxx has the following characteristics:

- Each bit of any register can be set, cleared, or tested directly.

- Any I/O Register can be accessed as a general-purpose register. That is, the same instruction set that accesses the general-purpose register can operate under I/O register.

# 2 Quick Reference to Instruction Details

| Instruction | Description                                       | Go to Page |

|-------------|---------------------------------------------------|------------|

| ADD         | Add                                               | 12         |

| AND         | And                                               | 10         |

| BC          | Bit Clear                                         | 19         |

| BS          | Bit Set                                           | 19         |

| CALL        | Subroutine Call                                   | 20         |

| CLR         | Clear Register                                    | 8          |

| CLRA        | Clear the A Register                              | 7          |

| СОМ         | Complement R                                      | 13         |

| СОМА        | Complement R, Place in A                          | 13         |

| DAA         | Decimal Adjust                                    | 3          |

| DEC         | Decrement R                                       | 9          |

| DECA        | Decrement R, Place in A                           | 9          |

| DISI        | Disable Interrupt                                 | 4          |

| DJZ         | Decrement R, Skip if "0"                          | 15         |

| DJZA        | Decrement R, Place in the A Register, Skip if "0" | 15         |

| ENI         | Enable Interrupt                                  | 4          |

| INC         | Increment R                                       | 14         |

| INCA        | Increment R, Place in the A Register              | 13         |

| INT         | Software Interrupt                                | 21         |

#### (Continuation)

| Instruction | Description                                           | Go to Page |

|-------------|-------------------------------------------------------|------------|

| JBC         | Bit Test, Skip if Clear                               | 19         |

| JBS         | Bit Test, Skip if Set                                 | 20         |

| JMP         | Unconditional Branch                                  | 21         |

| JZ          | Increment R, Skip if "0"                              | 18         |

| JZA         | Increment R, Place in the A Register, Skip if "0"     | 18         |

| LCALL       | Subroutine Call                                       | 22         |

| LJMP        | Unconditional Branch                                  | 22         |

| MOV         | Move Data                                             | 7          |

| NOP         | No Operation                                          | 3          |

| OR          | Inclusive OR                                          | 9          |

| RET         | Return from Subroutine                                | 5          |

| RETI        | Return from Interrupt                                 | 5          |

| RETL        | Return Immediate Data to A Register                   | 6          |

| RLC         | Rotate Left R through Carry                           | 17         |

| RLCA        | Rotate Left R through Carry, Place in the A Register  | 17         |

| RRC         | Rotate Right R through Carry                          | 16         |

| RRCA        | Rotate Right R through Carry, Place in the A Register | 16         |

| SLEP        | Seep                                                  | 3          |

| SUB         | Subtract                                              | 8          |

| SWAP        | Swap R                                                | 18         |

| SWAPA       | Swap R, Place in the A Register                       | 17         |

| TBRD        | Table Read                                            | 23         |

| WDTC        | Clear Watchdog Timer                                  | 4          |

| XOR         | Exclusive OR                                          | 11         |

#### 3 **Instruction Description**

#### NOP (No Operation)

| Syntax          | NOP                                      |

|-----------------|------------------------------------------|

| Operation       | No Operation                             |

| Status Affected | None                                     |

| Description     | No operation. NOP is used for time delay |

| Example |            |                                  |

|---------|------------|----------------------------------|

| Example |            | ls pulse (system clock = 2 MHz): |

|         | BS 0x5,0x0 | ;P50 output high                 |

|         | NOP        | ;Delay 2 instruction cycles      |

|         | NOP        |                                  |

|         | BC 0x5,0x0 | ;P50 output low                  |

#### DAA (Decimal Adjust)

| Syntax          | DAA                                                                                                                                                                  |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation       | if $[A<3:0>>9].OR.[DC=1]$<br>then $A<3:0>+6 \rightarrow A<3:0>$ ;<br>if $[A<7:4>>9].OR.[C=1]$<br>then $A<7:4>+6 \rightarrow A<7:4>$ ;                                |

| Status Affected | C                                                                                                                                                                    |

| Description     | DAA adjusts the 8-bit value in the accumulator resulting from<br>an earlier addition of two variables (each in packed-BCD<br>format), and produces two 4-bit digits. |

| Example | Perform a decimal 6+9 operation: |

|---------|----------------------------------|

| -       | MOV A,@0x6                       |

|         | MOV 0x10,A                       |

|         | MOV A,@0x9                       |

|         | ADD A, $0x10$ ; $A = 0xf$        |

|         | DAA ;A = 15H (packed BCD)        |

#### SLEP (Sleep)

| Syntax          | SLEP                                                                                                                                                                                                                                                                                                                       |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation       | $\begin{array}{c} 00h \rightarrow WDT \\ 0 \rightarrow WDT \ Prescaler \\ 0 \rightarrow P \\ 1 \rightarrow T \end{array}$                                                                                                                                                                                                  |

| Status Affected | Р, Т                                                                                                                                                                                                                                                                                                                       |

| Description     | The Watchdog Timer is reset. If the prescaler is assigned to<br>the WDT, the prescaler is reset. The Power-down Status<br>Affected (P) is cleared and the Time-out Status Affected (T) is<br>set. The processor goes into SLEEP mode with the oscillator<br>stopped. See the data sheet on SLEEP mode for more<br>details. |

|                 |                                                                                                                                                                                                                                                                                                                            |

| Example         | SLEP ; The processor is put into SLEEP mode                                                                                                                                                                                                                                                                                |

#### ■ WDTC (Clear Watchdog Timer)

| Syntax          | WDTC                                                                                                                                                                              |  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Operation       | $\begin{array}{l} 00h \rightarrow WDT \\ 0 \rightarrow WDT \mbox{ Prescaler} \\ 1 \rightarrow P \\ 1 \rightarrow T \end{array}$                                                   |  |

| Status Affected | P, T                                                                                                                                                                              |  |

| Description     | The Watchdog Timer is reset. If the prescaler is assigned to the WDT, the prescaler is reset. The Power-down Status Affected (P) is set. The Time-out Status Affected (T) is set. |  |

|                 |                                                                                                                                                                                   |  |

| Example         | WDTC ;Clear the Watchdog Timer counter                                                                                                                                            |  |

#### ■ ENI (Enable Interrupt)

| Syntax          | ENI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation       | $1 \rightarrow INT$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Status Affected | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Description     | Enable interrupt by setting the INT bit. The INT is a global<br>interrupt enable bit.<br>There are several interrupt sources, e.g., internal TCC<br>overflow interrupt, external INT pin interrupt, Port pin<br>changed interrupt, and so on. When one of these interrupts<br>occurs, the processor will perform an interrupt phase. First, it<br>will push the present PC into the top of the stack and reset the<br>INT flag to disable further interrupt. Then it will set the PC to<br>the corresponding interrupt vector, fetch the related code,<br>and execute. The Interrupt Status Register (Register 0xf)<br>indicates the interrupt source. |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Fxample         | FNI · Fnable interrunt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Example | ENI ; Enable interrupt<br>After Instruction |

|---------|---------------------------------------------|

|         | Bit 6 of CONT register : 1                  |

#### ■ DISI (Disable Interrupt)

| Syntax          | DISI                                                                                 |

|-----------------|--------------------------------------------------------------------------------------|

| Operation       | $0 \rightarrow INT$                                                                  |

| Status Affected | None                                                                                 |

| Description     | Disable interrupt by clearing the INT bit. The INT is a global interrupt enable bit. |

|                 |                                                                                      |

| Example | DISI ; Disable interrupt   |

|---------|----------------------------|

|         | After Instruction          |

|         | Bit 6 of CONT register : 0 |

#### ■ RET (Return from Subroutine)

| Syntax          | RET                                                                                     |

|-----------------|-----------------------------------------------------------------------------------------|

| Operation       | $[Top of Stack] \to PC$                                                                 |

| Status Affected | None                                                                                    |

| Description     | Return from subroutine. Stack is popped and the top of the stack is loaded into the PC. |

| Example | TEST:                       |

|---------|-----------------------------|

|         | •                           |

|         |                             |

|         |                             |

|         | RET                         |

|         | •                           |

|         | •                           |

|         | CALL TEST                   |

|         | HERE ADD A,@0x1             |

|         | •                           |

|         | •                           |

|         |                             |

|         | Before Instruction          |

|         | Top of Stack = address HERE |

|         | After Instruction           |

|         | PC = address HERE           |

#### ■ RETI (Return from Interrupt)

| Syntax          | RETI                                                                                                                                                                                        |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation       | $\begin{array}{l} [Top of Stack] \to PC \\ 1 \to INT \end{array}$                                                                                                                           |

| Status Affected | None                                                                                                                                                                                        |

| Description     | Return from interrupt routine. The stack is popped and the top of the stack is loaded into the PC. The interrupt is enabled by setting the INT bit. The INT is global interrupt enable bit. |

| Example | INTRIN: ;Interrupt routine                                                                                    |

|---------|---------------------------------------------------------------------------------------------------------------|

|         | RETI<br>MAIN:                                                                                                 |

|         | ;Interrupt occurs<br>HERE:                                                                                    |

|         | Before Instruction<br>[Top of Stack] = address HERE<br>After Instruction<br>PC = address HERE<br>INT flag = 1 |

#### ■ RETL (Return Immediate Data to A Register)

| Syntax          | RETL k                                                                                                                                                 |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation       | $k \rightarrow A$                                                                                                                                      |

|                 | $[Top of Stack] \to PC$                                                                                                                                |

| Status Affected | None                                                                                                                                                   |

| Description     | Return from subroutine. The immediate data "k" is loaded<br>into the A register. The stack is popped and the top of the<br>stack is loaded into the PC |

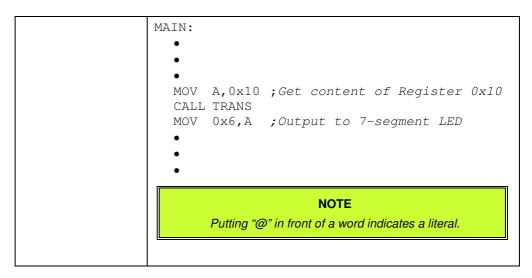

| Example | <pre>xample Perform a 7-segment LED translation table<br/>The 7-segment LED connected to Port 6.<br/>;Define the register<br/>PC == 2</pre> |                      |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

|         | TRANS:<br>ADD PC,A                                                                                                                          |                      |

|         | RETL @0b11111100<br>RETL @0b01100000                                                                                                        | BIT 7                |

|         | RETL @0b11011010                                                                                                                            | ВІТ 2<br>ВІТ 1 ВІТ 6 |

|         | RETL @0b11110010<br>RETL @0b01100110                                                                                                        | вп з Вп 5            |

|         | RETL @0b10110110<br>RETL @0b10111110                                                                                                        |                      |

|         | RETL @0b11100000<br>RETL @0b1111110                                                                                                         | BIT 4 BIT 0          |

|         | REIL @OBIIIIIIO<br>REIL @Ob11110110                                                                                                         |                      |

#### MOV (Move Data)

| Syntax          | MOV R,A                                                                                                                |

|-----------------|------------------------------------------------------------------------------------------------------------------------|

| Operation       | $A \rightarrow R$                                                                                                      |

| Status Affected | None                                                                                                                   |

| Description     | Move the contents of the A register to R                                                                               |

|                 |                                                                                                                        |

| Syntax          | MOV A,R                                                                                                                |

| Operation       | $R \rightarrow A$                                                                                                      |

| Status Affected | Z                                                                                                                      |

| Description     | Move the contents of R to the A register. If the result is "0", Z flag will be set. Otherwise, Z flag will be cleared. |

| Syntax          | MOV R,R                      |

|-----------------|------------------------------|

| Operation       | $R \rightarrow R$            |

| Status Affected | Z                            |

| Description     | Move the contents of R to R. |

| Syntax          | MOV A,k                                                  |

|-----------------|----------------------------------------------------------|

| Operation       | $k \rightarrow A$                                        |

| Status Affected | None                                                     |

| Description     | Load immediate data (8-bit literal) into the A register. |

| Example | Move data from accumulator to register: |

|---------|-----------------------------------------|

|         | MOV A,@0x11 ;Move immediate data to A   |

|         | MOV 0x10,A ;Move data from A to R       |

|         | MOV A,9 ;Move data from R to A          |

|         | MOV 0x10,0x10 ;Z flag is 0              |

#### ■ CLRA (Clear the A Register)

| Syntax          | CLRA                             |

|-----------------|----------------------------------|

| Operation       | $0 \rightarrow A$                |

| Status Affected | $1 \rightarrow Z$                |

| Description     | Reset Accumulator. Z flag is set |

## ■ CLR (Clear Register)

| Syntax          | CLR R                            |  |

|-----------------|----------------------------------|--|

| Operation       | $0 \rightarrow R$                |  |

| Status Affected | $1 \rightarrow Z$                |  |

| Description     | Reset Register R. Z flag is set. |  |

|                 |                                  |  |

| Example         | CLR 0x10 ;Reset Register 0x10    |  |

#### ■ SUB (Subtract)

| Syntax          | SUB A,R                                                                                      |

|-----------------|----------------------------------------------------------------------------------------------|

| Operation       | $R - A \rightarrow A$                                                                        |

| Status Affected | Z,C,DC                                                                                       |

| Description     | Subtract the A register from R register. The result is placed in the A register.             |

|                 |                                                                                              |

| Syntax          | SUB R,A                                                                                      |

| Operation       | $R - A \rightarrow R$                                                                        |

| Status Affected | Z, C, DC                                                                                     |

| Description     | Subtract the A register from R register. The result is placed in the R register.             |

|                 |                                                                                              |

| Syntax          | SUB A,k                                                                                      |

| Operation       | $k - A \to A$                                                                                |

| Status Affected | Z, C, DC                                                                                     |

| Description     | Subtract the A register from the immediate data "k". The result is placed in the A register. |

| Example | The following co<br>A = $0x99-0x55$ : | des illustrate how to obtain                    |

|---------|---------------------------------------|-------------------------------------------------|

|         | MOV A,@0x99                           |                                                 |

|         | MOV 0x10,A                            | ;R <b>10</b> = 0x99                             |

|         | MOV A,@0x55                           |                                                 |

|         | SUB A,0x10                            | $; A = 0 \times 44$                             |

|         | The following co                      | des illustrate how to obtain                    |

|         | A = 0x02 - A:                         |                                                 |

|         | MOV A,@0x01                           | ;A = 0x01                                       |

|         | SUB A,@0x02                           | $; A = 0 \times 02 - 0 \times 01 = 0 \times 01$ |

|         |                                       | ;C flag = 1 , result is                         |

|         |                                       | ;positive                                       |

#### ■ DECA (Decrement R, Place in A)

| Syntax          | DECA R                                                       |

|-----------------|--------------------------------------------------------------|

| Operation       | $R - 1 \rightarrow A$                                        |

| Status Affected | Z                                                            |

| Description     | Decrease the R register. The result is placed in A register. |

| Example | The following codes illustrate how to make a 16 - iteration loop:                 |

|---------|-----------------------------------------------------------------------------------|

|         | STATUS == 3 ;Status Register<br>Z_FLAG == 2<br>MOV A,@0x10<br>MOV 0x10,A<br>LOOP: |

|         | DECA 0x10<br>MOV 0x10,A<br>JBS STATUS,Z_FLAG<br>JMP LOOP                          |

#### ■ DEC (Decrement R)

| Syntax          | DEC R                    |

|-----------------|--------------------------|

| Operation       | $R - 1 \rightarrow R$    |

| Status Affected | Z                        |

| Description     | Decrease the R register. |

| Example | The following codes illustrate how to make a 16 - Iteration loop:                                                    |

|---------|----------------------------------------------------------------------------------------------------------------------|

|         | <pre>STATUS == 3 ;Status Register Z_FLAG == 2 MOV A,@0x10 MOV 0x10,A LOOP: DEC 0x10 JBS STATUS,Z_FLAG JMP LOOP</pre> |

#### ■ OR (Inclusive OR)

| Syntax          | OR A,R                                                                                                  |

|-----------------|---------------------------------------------------------------------------------------------------------|

| Operation       | $A \lor R \to A$                                                                                        |

| Status Affected | Z                                                                                                       |

| Description     | Inclusive OR the contents of A register with the R register.<br>The result is placed in the A register. |

| Syntax          | OR R,A                                                                                       |                                                                                                                                                                                   |

|-----------------|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation       | $A \lor B \to B$                                                                             |                                                                                                                                                                                   |

| -               |                                                                                              |                                                                                                                                                                                   |

| Status Affected | Z                                                                                            |                                                                                                                                                                                   |

| Description     | Inclusive OR the cont<br>The result is placed in                                             | ents of the A register with R register.<br>h the R register                                                                                                                       |

| Syntax          | OR A,k                                                                                       |                                                                                                                                                                                   |

| Operation       | $A \lor k \to A$                                                                             |                                                                                                                                                                                   |

| Status Affected | Z                                                                                            |                                                                                                                                                                                   |

| Description     |                                                                                              | ents of the A register with the immediate<br>The result is placed in the A register                                                                                               |

|                 |                                                                                              |                                                                                                                                                                                   |

| Example         | A = 0x55 + 0xAA MOV A, @0x55 MOV 0x10, A MOV A, @0xAA OR A, 0x10 or MOV A, @0x55 OR A, @0xAA | ;R10 = $0x55 + 0xAA$<br>;A = $0xAA + 0x55 = 0xFF$ ,<br>;Z flag = 0<br>;k = $0xAA$ , A = $0x55 + 0xAA =$<br>; $0xFF$ , Z flag = 0<br>odes illustrate how to obtain<br>A = $0xFF$ : |

## AND (And)

| Syntax          | AND A,R                                                                                         |

|-----------------|-------------------------------------------------------------------------------------------------|

| Operation       | $A \& R \rightarrow A$                                                                          |

| Status Affected | Z                                                                                               |

| Description     | AND the contents of the A register with the R register. The result is placed in the A register. |

| Syntax          | AND R,A                                                                                     |

|-----------------|---------------------------------------------------------------------------------------------|

| Operation       | $A \And R \to R$                                                                            |

| Status Affected | Z                                                                                           |

| Description     | AND the contents of the A register with the R register. The result is placed in R register. |

| Syntax          | AND A,K                                                                                                            |  |

|-----------------|--------------------------------------------------------------------------------------------------------------------|--|

| Operation       | $A \And K \to A$                                                                                                   |  |

| Status Affected | Z                                                                                                                  |  |

| Description     | AND the contents of the A register with the immediate data specified by K. The result is placed in the A register. |  |

|                 |                                                                                                                    |  |

| Example         | AND Port 6 with the R <b>10</b> register, then output                                                              |  |

| Example | AND Port 6 with th    | e R <b>10</b> register, then output |  |

|---------|-----------------------|-------------------------------------|--|

|         | the result to Port 6: |                                     |  |

|         | MOV A,0x6             | ;Input from Port 6                  |  |

|         | AND A, 0x10           | ;AND with R <b>10</b>               |  |

|         | MOV 0x6,A             | ;Output to Port 6                   |  |

|         | R10 = R11  AND  R12   |                                     |  |

|         | MOV A, 0x11           |                                     |  |

|         | MOV 0x10,A            |                                     |  |

|         | MOV A, 0x12           |                                     |  |

|         | AND 0x10,A            | ;R10 = R11 AND R12                  |  |

## ■ XOR (Exclusive OR)

| Syntax          | XOR A,R                                                                                                   |

|-----------------|-----------------------------------------------------------------------------------------------------------|

| Operation       | $A \oplus R \to A$                                                                                        |

| Status Affected | Z                                                                                                         |

| Description     | The contents of the A register are XOR'ed with the R register.<br>The result is placed in the A register. |

| Syntax          | XOR R,A                                                                              |

|-----------------|--------------------------------------------------------------------------------------|

| Operation       | $A \oplus R \to R$                                                                   |

| Status Affected | Z                                                                                    |

| Description     | Exclusive OR the A register with the R register. The result is placed in R register. |

| Syntax          | XOR A,k                                                                                        |

|-----------------|------------------------------------------------------------------------------------------------|

| Operation       | $A \oplus k \to A$                                                                             |

| Status Affected | Z                                                                                              |

| Description     | Exclusive OR the A register with the immediate data k. The result is placed in the A register. |

| Example | Check whether the content of Register 0x10 is 0x55. If not, jump to ERROR subroutine: |

|---------|---------------------------------------------------------------------------------------|

|         | STATUS == 3                                                                           |

|         | $Z_FLAG == 2$                                                                         |

|         | MOV A,@0x55                                                                           |

|         | XOR A,0x10                                                                            |

|         | JBS STATUS,Z_FLAG                                                                     |

|         | JMP ERROR                                                                             |

|         | The following codes get R <b>10</b> = R <b>11</b> XOR R <b>12:</b>                    |

|         | MOV A,0x11                                                                            |

|         | MOV 0x10,A                                                                            |

|         | MOV A,0x12                                                                            |

|         | XOR 0x10,A ;R10 = R11 XOR R12                                                         |

|         | The following codes get $A = A XOR 0 xF0$ :                                           |

|         | MOV A, $@0 \times 00$ ; $A = 0 \times 00$                                             |

|         | XOR A, $@0xF0$ ; $A = 0xF0$                                                           |

#### ■ ADD (Add)

| Syntax          | ADD A,R                                                                                                |

|-----------------|--------------------------------------------------------------------------------------------------------|

| Operation       | $A + R \rightarrow A$                                                                                  |

| Status Affected | Z,C,DC                                                                                                 |

| Description     | The contents of the A register are added to the R register.<br>The result is placed in the A register. |

| Syntax          | ADD R,A                                                                                   |

|-----------------|-------------------------------------------------------------------------------------------|

| Operation       | $A + R \rightarrow R$                                                                     |

| Status Affected | Z,C,DC                                                                                    |

| Description     | ADD the contents of the A register to the R register. The result is placed in register R. |

| Syntax          | ADD A,k                                                                                                       |

|-----------------|---------------------------------------------------------------------------------------------------------------|

| Operation       | $K + A \to A$                                                                                                 |

| Status Affected | Z,C,DC                                                                                                        |

| Description     | The contents of the A register are added with the immediate data "k". The result is placed in the A register. |

| Example | The fol | lowing codes | get A = R <b>11</b> + R <b>12:</b>           |

|---------|---------|--------------|----------------------------------------------|

|         | MOV     | A,0x11       |                                              |

|         | ADD     | A,0x12       | ;A = R <b>11</b> + R <b>12</b>               |

|         | The fol | lowing codes | get R <b>10</b> = R <b>11</b> + R <b>12:</b> |

|         | MOV     | A,0x11       |                                              |

|         | MOV     | 0x10,A       |                                              |

|         | MOV     | A,0x12       |                                              |

|         | ADD     | 0x10,A       | ;R10 = R11 + R12                             |

|         | The fol | lowing codes | get $A = 0x01 + 0x01$ :                      |

|         | MOV     | A,@0x01      | ;A = 0x01                                    |

|         | ADD     | A,@0x01      | ; $A = 0 \times 02$                          |

#### ■ COMA (Complement R, Place in A)

| Syntax          | COMA R                                                                                   |

|-----------------|------------------------------------------------------------------------------------------|

| Operation       | $\overline{R} \to A$                                                                     |

| Status Affected | Z                                                                                        |

| Description     | The contents of the R register are complemented. The result is placed in the A register. |

| Example | Input from Port 6, complement the contents; then output the result to Port 6: |  |

|---------|-------------------------------------------------------------------------------|--|

|         | MOV A,0x6<br>MOV 0x10,A                                                       |  |

|         | COMA 0x10<br>MOV 0x6,A                                                        |  |

#### ■ COM (Complement R)

| Syntax          | COM R                                                                                                                                           |  |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Operation       | $\overline{R} \to R$                                                                                                                            |  |

| Status Affected | Z                                                                                                                                               |  |

| Description     | The contents of the R register are complemented. The result is placed in register R.                                                            |  |

|                 |                                                                                                                                                 |  |

| Example         | The following codes complement the contents of<br>R <b>10:</b><br>MOV A,@0x11<br>MOV 0x10,A ;R <b>10</b> = 0x11<br>COM 0x10 ;R <b>10</b> = 0xEE |  |

#### ■ INCA (Increment R, Place in the A Register)

| Syntax          | INCA R                                                                                  |

|-----------------|-----------------------------------------------------------------------------------------|

| Operation       | $R + 1 \rightarrow A$                                                                   |

| Status Affected | Z                                                                                       |

| Description     | The contents of the R register are incremented. The result is placed in the A register. |

|         | 1        |                  |                           |

|---------|----------|------------------|---------------------------|

| Example | Counts t | the external     | interrupt. When count is  |

|         | up to 10 | 00 times, som    | me flags are set:         |

|         | STATUS   | $== 0 \times 03$ | ;Status Register          |

|         |          | == 0x0f          | -                         |

|         |          | $== 0 \times 10$ | ,                         |

|         | -        | $== 0 \times 11$ |                           |

|         |          |                  | ;Buffer of A              |

|         | —        | == 0x13          |                           |

|         |          |                  | ; Time out flag           |

|         |          |                  | ;TCC interrupt flag       |

|         |          | == 3             | ;External interrupt flag  |

|         | Z_FLAG   |                  | , incernar incertape itag |

|         | EXT INT  |                  |                           |

|         | DISI     |                  | ;Disable interrupt        |

|         | BC       | ISR, EXIF        | ;Reset EXIF flag          |

|         |          | A_BUF,A          |                           |

|         |          | A, STATUS        |                           |

|         | MOV      | S_BUF,A          | ;Backup Status Register   |

|         |          |                  | ;Increment count          |

|         | MOV      | COUNTER, A       |                           |

|         | XOR      | A,@100           | ;If count to 100, set     |

|         |          |                  | ;TMO_FLG                  |

|         | JBC      | STATUS,Z_FL      | AG                        |

|         | BS       | FLAG, TMO_FL     | G                         |

|         | MOV      | A,S_BUF          |                           |

|         | MOV      | STATUS,A         | ;Restore Status Register  |

|         | MOV      | A,A_BUF          | ;Restore A. C flag in     |

|         |          |                  | ;STATUS is affected       |

|         | BC       | STATUS,Z_FL      | G                         |

|         | JBC      | S_BUF,Z_FLG      | ;Obtain the REAL C flag   |

|         | BS       | STATUS,Z_FL      | G                         |

|         | RTI      |                  |                           |

## ■ INC (Increment R)

| Syntax          | INC R                                           |

|-----------------|-------------------------------------------------|

| Operation       | $R + 1 \rightarrow R$                           |

| Status Affected | Z                                               |

| Description     | The contents of the R register are incremented. |

|                 |                                                 |

| Example | MOV A,@0x11 |        |                     |

|---------|-------------|--------|---------------------|

|         | MOV         | 0x10,A | ;R <b>10</b> = 0x11 |

|         | INC         | 0x10   | ;R <b>10</b> = 0x12 |

#### ■ DJZA (Decrement R, Place in the A Register, Skip if "0")

| Syntax          | DJZA R                                                                                                                                                                      |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation       | $R-1 \rightarrow A$ , skip if "0"                                                                                                                                           |

| Status Affected | None                                                                                                                                                                        |

| Description     | Decrease the contents of the R register. The result is placed<br>in the A register.<br>If the result is "0", the next instruction which is already fetched<br>is discarded. |

| r       | I                                 |  |  |

|---------|-----------------------------------|--|--|

| Example | HERE:                             |  |  |

|         | DJZA 0x9                          |  |  |

|         | CONT:                             |  |  |

|         | MOV A,0x10                        |  |  |

|         | SKIP:                             |  |  |

|         | ADD A,010                         |  |  |

|         | Before Instruction                |  |  |

|         | PC = address HERE                 |  |  |

|         | After Instruction                 |  |  |

|         | A=R9-1                            |  |  |

|         | if $A = 0$ , PC = address SKIP    |  |  |

|         | if $A \neq 0$ , PC = address CONT |  |  |

#### ■ DJZ (Decrement R, Skip if "0")

| Syntax          | DJZ R                                                                                                                                                                  |  |  |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Operation       | $R - 1 \rightarrow R$ , skip if "0"                                                                                                                                    |  |  |

| Status Affected | None                                                                                                                                                                   |  |  |

| Description     | The contents of the R register are decreased. The result is placed in register R.<br>If the result is "0", the next instruction which is already fetched is discarded. |  |  |

|                 |                                                                                                                                                                        |  |  |

| Example         | MOV A, @100<br>MOV 0x10, A<br>LOOP:                                                                                                                                    |  |  |

|                 | DJZ 0x10 ;Decrement R <b>10</b> . If the result<br>;is not "0", executes the JMP<br>;instruction, else skip the JMP<br>;instruction.                                   |  |  |

JMP LOOP

| Syntax          | RRCA R                                                                                                                                                        |  |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Operation       | $R(n) \to A(n\text{-}1), \ R(0) \to C, \ C \to A(7)$                                                                                                          |  |

| Status Affected | С                                                                                                                                                             |  |

| Description     | The contents of the R register are rotated 1-bit to the right through the Carry Flag. The result is placed in the A register.<br>C A(7) A(6:0)<br>R(7:1) R(0) |  |

#### ■ RRCA (Rotate Right R through Carry, Place in the A Register)

| Example | The following codes perform how to rotate a register to the right (not to include C flag) and output the result to Port 5: |                       |  |  |  |

|---------|----------------------------------------------------------------------------------------------------------------------------|-----------------------|--|--|--|

|         | BIT_BUF == 10                                                                                                              |                       |  |  |  |

|         | COUNTER == 11                                                                                                              | —                     |  |  |  |

|         | MOV A,@0x8                                                                                                                 |                       |  |  |  |

|         | MOV COUNTER,A                                                                                                              |                       |  |  |  |

|         | LOOP:                                                                                                                      |                       |  |  |  |

|         | RRCA BIT_BUF                                                                                                               | ;Shift the LSB to C   |  |  |  |

|         | RRCA BIT_BUF                                                                                                               | ;Start right rotation |  |  |  |

|         | MOV 0x5,A                                                                                                                  |                       |  |  |  |

|         | MOV BIT_BUF,                                                                                                               | P                     |  |  |  |

|         | DJZ COUNTER                                                                                                                |                       |  |  |  |

|         | JMP LOOP                                                                                                                   |                       |  |  |  |

#### ■ RRC (Rotate Right R through Carry)

| Syntax          | RRC R                                                                                                                         |  |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------|--|

| Operation       | $R(n) \to R(n\text{-}1), \ R(0) \to C, \ C \to R(7)$                                                                          |  |

| Status Affected | С                                                                                                                             |  |

| Description     | The contents of the R register are rotated 1-bit to the right through the Carry Flag. The result is placed in the R register. |  |

| Example | MOV | A,@OxOf |                                |

|---------|-----|---------|--------------------------------|

|         | CLR | 0x3,0   | ;Clear C flag                  |

|         | MOV | 0x10,A  | ;R <b>10</b> = 00001111        |

|         | RRC | 0x10    | ;R <b>10</b> = 00000111, C = 1 |

#### ■ RLCA (Rotate Left R through Carry, Place in the A Register)

| Syntax          | RLCA R                                                                                                                                                         |  |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Operation       | $R(n) \to A(n+1), \ R(7) \to C, \ C \to A(0)$                                                                                                                  |  |

| Status Affected | C                                                                                                                                                              |  |

| Description     | The contents of the R register are rotated 1-bit to the left<br>through the Carry Flag. The result is placed in the A register.<br>A(7:1) A(0) C $R(7) R(6:0)$ |  |

| Example | Perform a rotate left operation of a 16-bit register (R <b>10</b> , R <b>11</b> ): |                                    |  |  |  |

|---------|------------------------------------------------------------------------------------|------------------------------------|--|--|--|

|         | RLCA 0x11                                                                          | ;Shift the MSB of R <b>11</b> into |  |  |  |

|         |                                                                                    | ;C flag                            |  |  |  |

|         | RLC 0x10                                                                           |                                    |  |  |  |

|         | RLC 0x11                                                                           |                                    |  |  |  |

#### ■ RLC (Rotate Left R through Carry)

| Syntax          | RLC R                                                                                                                        |

|-----------------|------------------------------------------------------------------------------------------------------------------------------|

| Operation       | $R(n) \to R(n{+}1),  R(7) \to C,  C \to R(0)$                                                                                |

| Status Affected | С                                                                                                                            |

| Description     | The contents of the R register are rotated 1-bit to the left through the Carry Flag. The result is placed in the R register. |

#### SWAPA (Swap R, Place in the A Register)

| Syntax          | SWAPA R                                                                                             |

|-----------------|-----------------------------------------------------------------------------------------------------|

| Operation       | $R(3:0) \rightarrow A(7:4)$<br>$R(7:4) \rightarrow A(3:0)$                                          |

| Status Affected | None                                                                                                |

| Description     | The upper and lower nibbles of register R are exchanged.<br>The result is placed in the A register. |

| Example | Swap the contents of Port 6: |

|---------|------------------------------|

|         | MOV A,0x6                    |

|         | MOV 0x10,A                   |

|         | SWAP 0x10                    |

|         | MOV 0x6,A                    |

#### ■ SWAP (Swap R)

|                 | ,                                                        |                   |              |  |

|-----------------|----------------------------------------------------------|-------------------|--------------|--|

| Syntax          | SWAP R                                                   |                   |              |  |

| Operation       | R(3:0) ⇔                                                 | R(7:4)            |              |  |

| Status Affected | None                                                     |                   |              |  |

| Description     | The upper and lower nibbles of Register R are exchanged. |                   |              |  |

|                 |                                                          |                   |              |  |

| Example         | MOV C                                                    | A,@0x43<br>)x10,A | ; R10 = 0x43 |  |

;R**10** = 0x34

#### ■ JZA (Increment R, Place in the A Register, Skip if "0")

0x10

SWAP

| Syntax          | JZA R                                                                                                                                                                        |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation       | $R + 1 \rightarrow A$ , skip if result = "0"                                                                                                                                 |

| Status Affected | None                                                                                                                                                                         |

| Description     | The contents of the R register are incremented. The result is placed in the A register.<br>If the result is "0", the next instruction which is already fetched is discarded. |

| Example | Port 6 | outputs | incremental | binary | signal: |

|---------|--------|---------|-------------|--------|---------|

|         | MOV    | A,@x00  |             |        |         |

|         | LOOP:  |         |             |        |         |

|         | MOV    | 0x6,A   |             |        |         |

|         | MOV    | 0x10,A  |             |        |         |

|         | JZA    | 0x10    |             |        |         |

|         | JMP    | LOOP    |             |        |         |

#### ■ JZ (Increment R, Skip if "0")

| Syntax          | JZ R                                                                                                                                                                        |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation       | $R + 1 \rightarrow R$ , skip if result = "0"                                                                                                                                |

| Status Affected | None                                                                                                                                                                        |

| Description     | Increase the contents of the R register. The result is placed<br>in the R register.<br>If the result is "0", the next instruction which is already fetched<br>is discarded. |

| Example | HERE:                                      |

|---------|--------------------------------------------|

|         | JZ 0x10                                    |

|         | CONT:                                      |

|         | MOV A,0x10                                 |

|         | SKIP:                                      |

|         | ADD A,010                                  |

|         | Before Instruction                         |

|         | PC = address HERE                          |

|         | After Instruction                          |

|         | R <b>10</b> = R <b>10</b> +1               |

|         | if R <b>10</b> = 0, PC = address SKIP      |

|         | if R <b>10</b> $\neq$ 0, PC = address CONT |

|         |                                            |

#### ■ BC (Bit Clear)

| Syntax          | BC R,b                          |  |

|-----------------|---------------------------------|--|

| Operation       | $0 \rightarrow R(b)$            |  |

| Status Affected | None                            |  |

| Description     | Bit "b" in Register R is reset. |  |

|                 |                                 |  |

| Example         | MOV A,@0x0f                     |  |

# Example MOV A, @0x0f MOV 0x10, A ;R10 = 00001111 BC 0x10, 3 ;R10 = 00000111

#### ■ BS (Bit Set)

| Syntax          | BSR,b                                  |

|-----------------|----------------------------------------|

| Operation       | $1 \rightarrow R(b)$                   |

| Status Affected | None                                   |

| Description     | Bit "b" in register R is set.          |

|                 |                                        |

| Example         | Cat the C flam in the Chatwa Demistary |

| Example | Set the | C flag | in th | e Status | Register: |

|---------|---------|--------|-------|----------|-----------|

|         | BS      | 0x3,2  |       |          |           |

#### ■ JBC (Bit Test, Skip if Clear)

| Syntax          | JBC R,b                                                                            |  |

|-----------------|------------------------------------------------------------------------------------|--|

| Operation       | if R(b) = "0", skip                                                                |  |

| Status Affected | None                                                                               |  |

| Description     | If bit "b" in Register R is "0", then the next instruction is skipped.             |  |

|                 |                                                                                    |  |

| Example         | Test the contents of R10. If "0", Port 5.0 outputs "0", else Port 5.0 outputs "1": |  |

|                 | JBC 0x10,0                                                                         |  |

|                 | BS 0x5,0                                                                           |  |

|                 | JBS 0x10,0                                                                         |  |

|                 | BC 0x5,0                                                                           |  |

#### ■ JBS (Bit Test, Skip if Set)

| Syntax          | JBS R,b                                                                |

|-----------------|------------------------------------------------------------------------|

| Operation       | if $R(b) = 1$ , skip                                                   |

| Status Affected | None                                                                   |

| Description     | If bit "b" in register R is "1", then the next instruction is skipped. |

| Example | HERE JE<br>CONT MC<br>SKIP AI | OV   | , -                                             |

|---------|-------------------------------|------|-------------------------------------------------|

|         | Before In<br>PC = addr        |      |                                                 |

|         |                               | = 0, | tion:<br>PC = address CONT<br>PC = address SKIP |

#### ■ CALL (Subroutine Call within one ROM Page)

| Syntax          | CALL k                                                                                                                                                                                                                                                                                                                                                   |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation       | PC + 1 → [Top of Stack]<br>$k \rightarrow PC(9:0)$<br>R3(7:5) → PC(12:10)                                                                                                                                                                                                                                                                                |

| Status Affected | None                                                                                                                                                                                                                                                                                                                                                     |

| Description     | When invoking a subroutine call, the return address is<br>pushed into the top of the stack first. Then the 10-bit address<br>specified by "k" is loaded into PC (9 : 0). The Page Select<br>Bits PS2, PS1, & PS0 (in R3, Status Register) are loaded into<br>PC (12 : 10). The CALL instruction can only call program<br>subroutine within one ROM page. |

| Example | HERE:<br>CALL SUBRTN                                                      |

|---------|---------------------------------------------------------------------------|

|         | CONT:<br>MOV A,@10                                                        |

|         | Before Instruction<br>PC = address HERE                                   |

|         | After Instruction<br>PC = address SUBRTN<br>[Top of Stack] = address CONT |

#### ■ JMP (Unconditional Branch)

| Syntax          | JMP k                                                                                                                                                                                                                                                                    |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation       | $\begin{array}{l} k \rightarrow PC(9:0) \\ R3(7:5) \rightarrow PC(12:10) \end{array}$                                                                                                                                                                                    |

| Status Affected | None                                                                                                                                                                                                                                                                     |

| Description     | When invoking an unconditional jump, the 10-bit address specified by "k" is loaded into PC (9 : 0). The Page Select Bits PS2, PS1, & PS0 (in R3, Status Register) are loaded into PC (12 : 10). The JMP instruction can only jump to any PC address within one ROM page. |

| Example | HERE JMP BRANCH                                                                      |

|---------|--------------------------------------------------------------------------------------|

|         | Before Instruction<br>PC = address HERE                                              |

|         | After Instruction<br>PC = address BRANCH                                             |

|         | <b>NOTE</b><br>Both PC addresses of HERE and BRANCH are within the<br>same ROM page. |

#### ■ INT (Software Interrupt)

| Syntax          | INT                                                                                                                     |

|-----------------|-------------------------------------------------------------------------------------------------------------------------|

| Operation       | PC + 1 → [Top of Stack]<br>0001H → PC                                                                                   |

| Status Affected | None                                                                                                                    |

| Description     | Invoke an interrupt subroutine. The return address (PC+1) is pushed into the top of the stack. The PC is set to 0x0001. |

| Example | ORG 0x001<br>JMP SET_INT<br>•           |

|---------|-----------------------------------------|

|         | SET_INT:                                |

|         | RETI<br>MAIN:                           |

|         | HERE INT                                |

|         | CONT CLRA                               |

|         | Before Instruction<br>PC = address HERE |

|         | After Instruction<br>PC = 0001H         |

|         | [Top of Stack] = address CONT           |

#### ■ LCALL (Subroutine Call)

| Syntax          | LCALL k                                                                                                                                                                                                                                                             |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation       | $\begin{array}{l} PC + 1 \rightarrow [Top \ of \ Stack] \\ k \rightarrow PC(15:0) \end{array}$                                                                                                                                                                      |

| Status Affected | None                                                                                                                                                                                                                                                                |

| Description     | When invoking a subroutine call, the return address is<br>pushed into the top of the stack first. Then the 15-bit address<br>specified by "k" is loaded into PC (15:0). The LCALL<br>instruction can call any program subroutine (without ROM<br>page restriction). |

| After Instruction<br>PC = address SUBRTN<br>[Top of Stack] = address CONT<br>NOTE   |

|-------------------------------------------------------------------------------------|

| The program subroutine SUBRTN can call any PC address without ROM page restriction. |

#### ■ LJMP (Unconditional Branch)

| Syntax          | LJMP k                                                                                                                                                                             |  |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Operation       | $k \rightarrow PC(15:0)$                                                                                                                                                           |  |

| Status Affected | None                                                                                                                                                                               |  |

| Description     | When invoking an unconditional jump, the 15-bit address specified by "k" is loaded into PC (15:0). The LJMP instruction can jump to any PC address (without ROM page restriction). |  |